## AlGaAs/GaAs HETEROJUNCTION BIPOLAR TRANSISTORS WITH 4W/mm POWER DENSITY AT X-BAND

B. Bayraktaroglu, N. Camilleri, H.D. Shih, and H. Q. Tserng

Texas Instruments Incorporated

POB 655936, M/S 134

Dallas TX 75265

ABSTRACT

Fabrication and microwave characterization of X-band AlGaAs/GaAs heterojunction bipolar transistors are described. MBE was used to prepare the device structure with heavily doped ( $1 \times 10^{19} \text{ cm}^{-3}$ ) 1000 Å thick base layers. Two 2 μm x 10 μm emitter fingers separated by 2 μm (total emitter periphery of 40 μm) were used in a self-aligned emitter-base configuration. From the S-parameter measurements  $f_t$  and  $f_{max}$  values of 25 and 20 GHz respectively were determined. Devices operating under CW conditions produced 80 mW CW output power (2W/mm of emitter periphery) with 4 dB gain and 23% power added efficiency at 10 GHz. Under 0.25 μs pulses, 160 mW output power (4 W/mm) was obtained with 4 dB gain and 35% power added efficiency.

INTRODUCTION

Heterojunction bipolar transistors (HBT) are currently being developed for microwave applications due to their superior high frequency performance over conventional Si bipolar transistors. The advantages of HBTs arise from the use of a heterojunction at the emitter-base interface which suppresses hole injection from the base into emitter. In HBTs, base layers can be doped very heavily (resulting in a low base resistance) without degrading emitter injection efficiency. Reduced base resistance and emitter charging time constant has drastically improved the high frequency performance of HBTs. Maximum frequency of oscillation,  $f_{max}$ , values of 70 GHz have been reported<sup>(1)</sup>.

Rapid progress is being made in the design and fabrication of HBTs. Progress has been made particularly in the areas of materials preparation (MBE and MOCVD) and the development of self-aligned fabrication techniques<sup>(2-4)</sup>. While further progress can be expected in the high frequency performance of HBTs, at X- and Ku-band frequencies HBTs now offer a real alternative to Si bipolar transistors and GaAs FETs. It has been shown that<sup>(5)</sup> at 4 GHz HBT oscillator phase noise characteristics are similar to that of Si bipolar transistors and superior to that of GaAs FETs.

Although the power performance of HBTs have not been studied in detail so far, there have been some reports of power performances that demonstrate the potential of HBTs. At 3 GHz, 320 mW CW and 500 mW pulses output powers were obtained<sup>(6)</sup>. At 12 GHz, 50 mW was demonstrated<sup>(5)</sup>. In this paper, the power performance of self-aligned, X-band AlGaAs/GaAs HBTs are reported.

DESIGN AND FABRICATION

The vertical structure of the device is shown in Figure 1. All epitaxial layers were grown by MBE on a (100) surface of an undoped semi-insulating (SI) substrate. Si and Be were used as the n- and p-type dopants, respectively. The emitter layer was made of  $\text{Al}_x\text{Ga}_{1-x}\text{As}$  with  $x=0.27$  and was doped to a level of  $2 \times 10^{17} \text{ cm}^{-3}$ . The base was doped heavily ( $1 \times 10^{19} \text{ cm}^{-3}$ ) to reduce base resistance. To avoid incorporation of p-type dopants into the emitter layer, a thin (100 Å) undoped "set back layer" was placed between the base and the emitter layers. The collector thickness and doping levels were chosen to yield a base-collector breakdown voltage of about 15 V.

|                 | Layer                  | Thickness (μm) | Doping (cm <sup>-3</sup> ) |

|-----------------|------------------------|----------------|----------------------------|

| <b>n+</b>       | Emitter Contact        | 0.3            | $5 \times 10^{18}$         |

| <b>n-AlGaAs</b> | Emitter ( $x = 0.27$ ) | 0.2            | $2 \times 10^{17}$         |

|                 | "Set-back" layer       | 0.01           | --                         |

| <b>p+</b>       | Base                   | 0.1            | $1 \times 10^{19}$         |

| <b>n</b>        | Collector              | 0.5            | $5 \times 10^{16}$         |

| <b>n+</b>       | Collector Contact      | 1.0            | $5 \times 10^{18}$         |

| <b>SI</b>       | Substrate              | 500            | --                         |

Figure 1 The vertical structure.

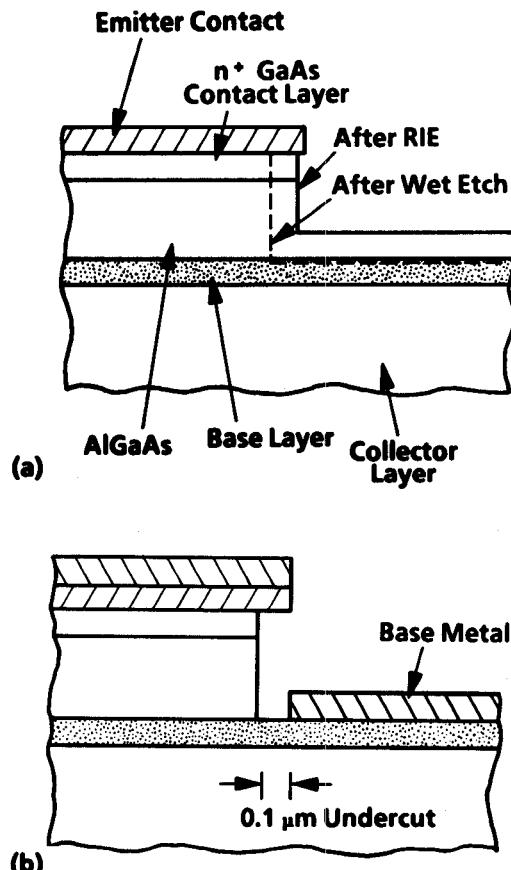

Two  $2 \mu\text{m} \times 10 \mu\text{m}$  emitter contacts placed  $2 \mu\text{m}$  apart were used for a total emitter periphery of  $40 \mu\text{m}$ . The base contact was self-aligned to the emitter contacts to minimize the external base resistance. Figure 2 illustrates the self-aligned fabrication technique. After the establishment of Au/Ge-Ni-Au contacts for emitter, the whole surface of the wafer was etched in a  $\text{BCl}_3$  plasma. The emitter contact metallization acts as an etch mask during this process, therefore the emitter layer under the contact is not etched. Extremely high aspect ratios can be obtained in  $\text{BCl}_3$  plasma<sup>(7)</sup>. The etch was stopped about  $0.1 \mu\text{m}$  from the base. The remaining emitter layer was removed in a weak  $\text{NaOH}:\text{H}_2\text{O}_2:\text{H}_2\text{O}$  solution. The accuracy of controlling the etch depth in this two-step process is about  $250 \text{ \AA}$  across a two inch wafer. Although the entire etch process can be accomplished using RIE only, we employed the wet etch step to produce a controlled amount of undercut. Wet etch also removes the plasma damaged surface of GaAs<sup>(8)</sup> ( $150 \text{ \AA}$  in our etch conditions). Base contact area was then defined around the emitter contact and Ti-Au was evaporated as shown in Figure 2. We consistently achieved a base contact-emitter layer edge separation of  $0.1 \mu\text{m}$  using this technique.

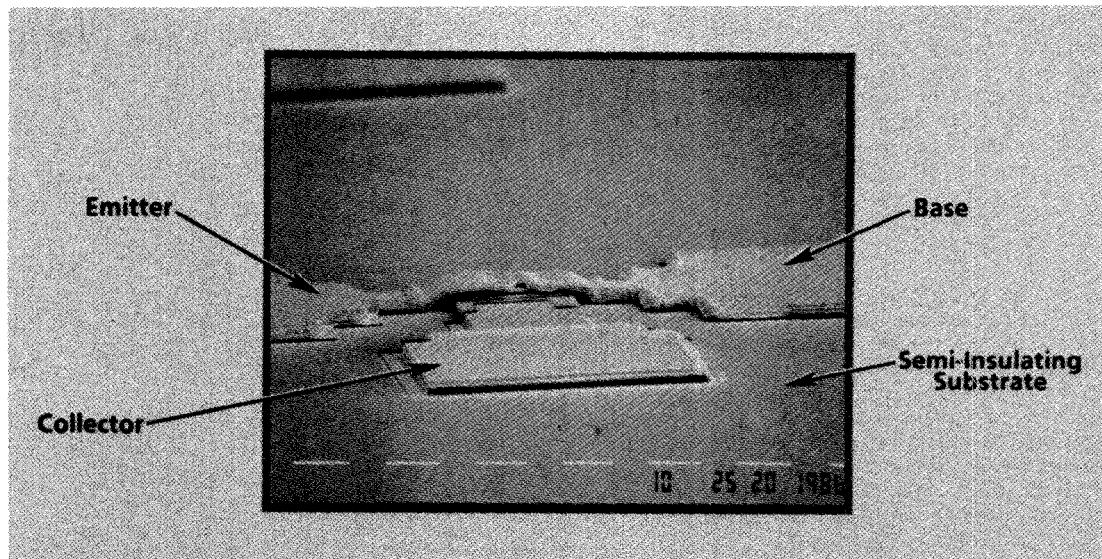

The device active area was isolated using mesa etching. AuGe-Ni-Au contacts were made to the collector layer. Miniature air bridges were used to connect all three electrodes of the device to their respective bonding pads placed on the SI surface of the wafer. An SEM picture of the completed device is shown in Figure 3.

#### RESULTS AND DISCUSSION

S-parameters of the device were measured both in common-emitter and common-base configurations. Using this data and computer aided design techniques, an equivalent circuit was derived. Measured and simulated

Figure 2 *The self aligned emitter base contact fabrication technique.*

Figure 3 *SEM picture of the  $40 \mu\text{m}$  emitter periphery device.*

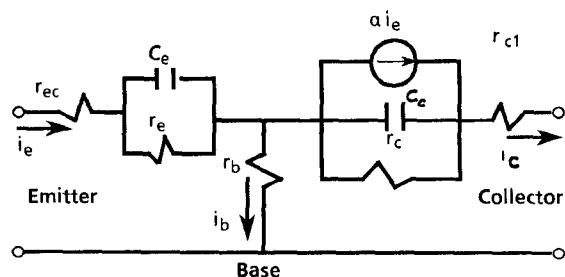

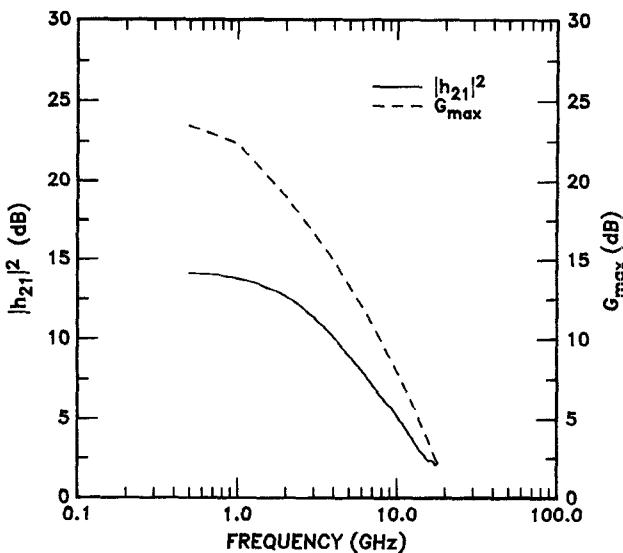

S-parameters were matched from 0.5 to 18 GHz. Figure 4 shows the equivalent circuit and the circuit element values for the device shown in Figure 3. From this model it is apparent that the most important factor limiting  $f_{max}$  is the collector capacitance ( $C_c$ ). Due to the self-aligned technique used in device fabrication, the base resistance,  $R_b$ , is kept small. The measured  $|h_{21}|^2$  and  $G_{max}$  values are plotted in Figure 5. The extrapolated values of  $f_t$  and  $f_{max}$  are 25 and 20 GHz, respectively.

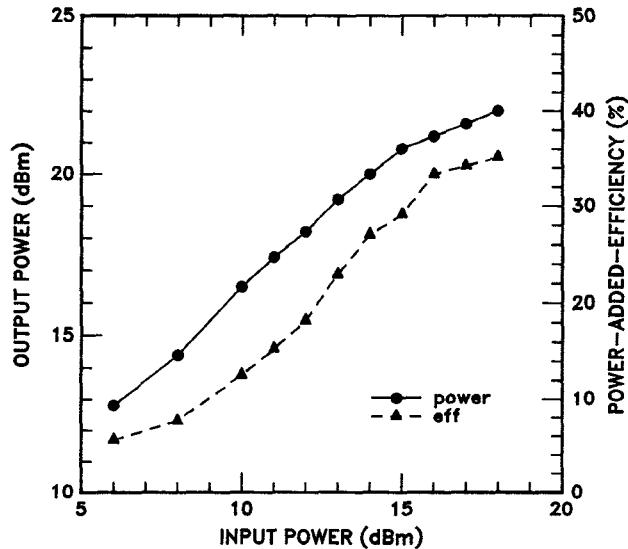

Power density measurements were made at 10 GHz with devices connected in common-base configuration. Under CW conditions the device produced 80 mW output power with 4 dB gain and 23% power added efficiency. This translates to a power density of 2 W/mm of emitter periphery. Under pulsed conditions (0.25  $\mu$ s pulse width and 5% duty cycle) devices produced 160 mW output power with 4 dB gain and 35% power added efficiency. This corresponds to a pulsed power density of 4 W/mm. The small signal gain was 6 dB. A plot of the measured 10 GHz pulsed output power and efficiency vs. input power is shown in Figure 6.

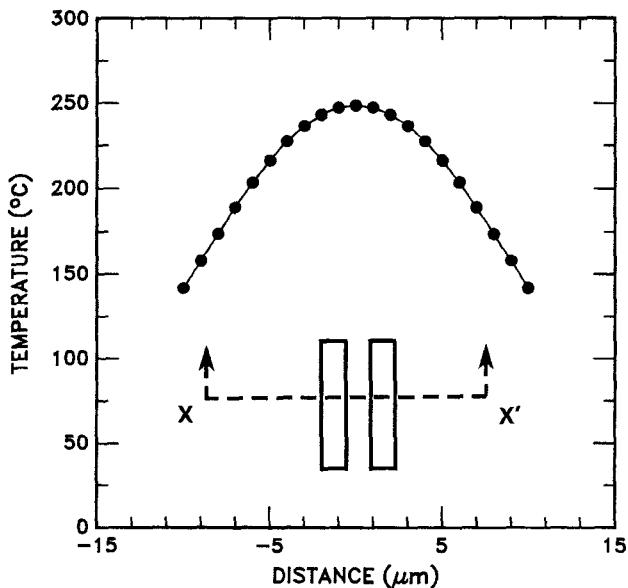

Substantial increases in the output power of HBTs under pulsed conditions compared to the CW case indicate that the devices are operating under thermally limited conditions. In that respect HBTs differ from GaAs FETs. In order to maximize the CW power capability of HBTs, careful attention must be paid to thermal designs. GaAs with its thermal conductivity approximately 1/3 of Si makes the thermal designs of HBTs more challenging than the design of Si transistors. A calculated temperature profile of the device under CW conditions (40 mW output power at 23% efficiency) is shown in Figure 7. It is clear that there is no thermal isolation between the emitter fingers. The device temperature is the highest at a point between the emitter fingers. The maximum temperature is about 250°C.

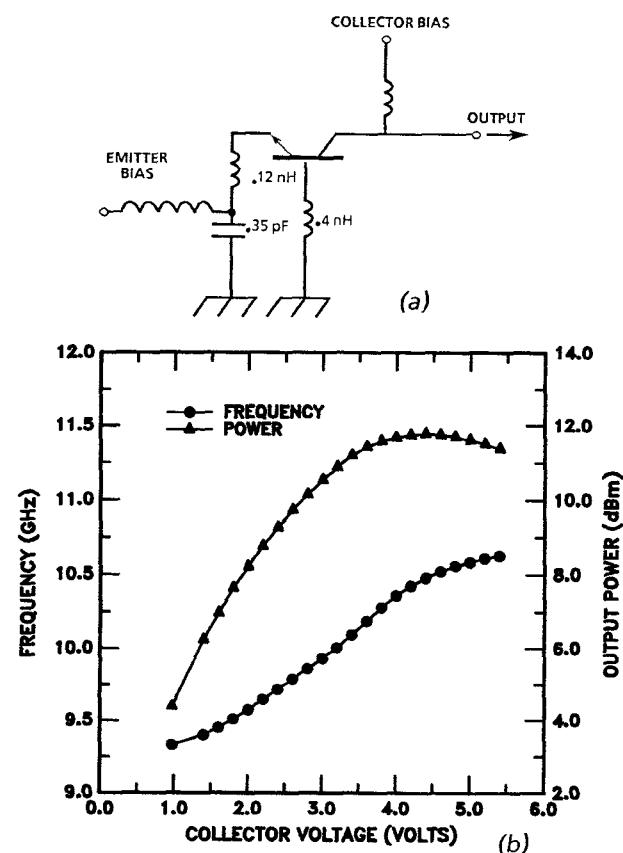

X-band oscillators have also been built and tested using these bipolar devices. The circuit topology of the hybrid oscillator is shown in Figure 8a. The device was configured in a common base mode and bond wire were used as inductors to cause feedback in the emitter base junction. The measured oscillator performance is shown in Figure 8b. The oscillation frequency tuning was achieved by varying the collector voltage (and therefore collector capacitance). A smooth tuning range of 1.25 GHz was obtained with a center frequency of 10 GHz. The output power was a maximum of 12 dBm at 10.4 GHz.

### CONCLUSIONS

High power density operation of MBE prepared AlGaAs/GaAs heterojunction bipolar transistors was demonstrated. Under CW and pulsed conditions, output power densities of 2 W/mm and 4 W/mm of emitter periphery respectively, were obtained at 10 GHz. Substantial increases in output power under pulsed conditions indicate that HBTs operate under thermally limited conditions. The maximum temperature within the device under CW conditions was estimated to be as high as 250°C. Compared to GaAs FETs operating at the same frequency, HBTs seem to offer two to four times the power density and five to ten times the packing density. Hybrid oscillators using HBTs gave a tuning range of 1.25 GHz at a center frequency of 10 GHz.

| Parameters            | Values    |

|-----------------------|-----------|

| $r_{ec}$ ( $\Omega$ ) | 11.0      |

| $C_e$ (pF)            | 0.2       |

| $r_e$ ( $\Omega$ )    | 9.0       |

| $r_b$ ( $\Omega$ )    | 2.5       |

| $C_c$ (pF)            | 0.22      |

| $a$                   | 0.8       |

| $r_{c1}$ ( $\Omega$ ) | 4.0       |

| $r_c$ ( $\Omega$ )    | 10,000.00 |

| $f_t$                 | 25 GHz    |

Figure 4 The equivalent circuit of 40  $\mu$ m emitter periphery device.

Figure 5 Measured  $|h_{21}|^2$  and  $G_{max}$  characteristics as a function of frequency.

#### ACKNOWLEDGMENTS

The authors would like to thank A. Elliot, A. R. Hernandez, and R. B. Smith for their technical assistance, D. J. McQuiddy, Jr. for his support and encouragements, and J. Fuller for typing this manuscript.

Figure 6 Pulsed output power and efficiency as a function of input power.

Figure 7 Calculated temperature profile across the device operating under CW conditions (80 mW output power with 23% power-added-efficiency).

Figure 8 (a) HBT oscillator characteristics

(b) The equivalent circuit

(b) Output power and frequency as a function of collector voltage.

#### REFERENCES

1. O. Nakajima, K. Nagata, Y. Yamauchi, H. Ito, and T. Ishibashi, "High-Avoltage AlGaAs/GaAs HBTs with Proton Implanted Buried Layers," *IEDM Techn. Digest*, pp. 266, 1986.

2. R. Fischer and H. Morkoc, "Reduction of Extrinsic Base Resistance in GaAs/AlGaAs Heterojunction Bipolar Transistors and Correlation with High-Frequency Performance," *IEEE Electron Dev. Lett.*, Vol. EDL-7, pp. 359, 1986.

3. M. F. Chang, P. M. Asbeck, K. C. Wang, G. J. Sullivan, and D. L. Miller, "AlGaAs/GaAs Heterojunction Bipolar Transistor Circuits with Improved High-Speed Performance," *Electronics Lett.*, Vol. 22, p. 1173, 1986.

4. K. Eda, M. Inada, Y. Ota, A. Nakagawa, T. Hirose, and M. Yanagihara, "Emitter-Base-Collector Self-Aligned Heterojunction Bipolar Transistors Using Wet Etching Process," *IEEE Electron. Dev. Lett.*, Vol. EDL-7, pp. 694, 1986.

5. K. K. Agarwal, "Dielectric Resonator Oscillators Using GaAs/(Ga,Al)As Heterojunction Bipolar Transistors," *IEEE MTT-S Technical Digest*, pp. 95, 1986.

6. B. Kim, H. Q. Tserng, S. K. Tiku, and H. D. Shih, "AlGaAs/GaAs Heterojunction Bipolar Power Transistors," *Electronics Lett.*, Vol. 21, pp. 258, 1985.

7. W. R. Frensel, B. Bayraktaroglu, S. E. Campbell, H. D. Shih, and R. E. Lehmann, "Design and Fabrication of a GaAs Vertical MESFET," *IEEE Trans. Electron Dev.*, Vol. ED-32, pp. 952, 1985.

8. K. Nagata, O. Nakajima, and T. Ishibashi, "Surface Damage of Reactive Ion Beam Etched GaAs," *Jap. J. Appl. Phys.*, Vol. 25, pp. L510, 1986.